# CXD2073Q

# **Digital Comb Filter (NTSC)**

#### Description

The CXD2073Q is an adaptive comb filter compatible with NTSC system, and provide high-precision Y/C separation with a single chip.

# Features

- Y/C separation by adaptive processing

- Horizontal aperture compensation circuit

- 8-bit A/D converter (1 channel)

- 8-bit D/A converter (2 channels)

- One 1H delay line

- 4 PLL

- Clamp circuit

# Absolute Maximum Ratings (Ta = 25°C, Vss = 0V)

| <ul> <li>Supply voltage</li> </ul> | DVdd     | Vss – 0.5 to +7.0     | V   |

|------------------------------------|----------|-----------------------|-----|

|                                    | DAVD     | Vss – 0.5 to +7.0     | V   |

|                                    | ADVD     | Vss – 0.5 to +7.0     | V   |

|                                    | PLVD     | Vss – 0.5 to +7.0     | V   |

| <ul> <li>Input voltage</li> </ul>  | Vi V     | /ss - 0.5 to VDD +0.5 | 5 V |

| <ul> <li>Output voltage</li> </ul> | Vo V     | /ss - 0.5 to VDD +0.5 | 5 V |

| Operating temperat                 | ure      |                       |     |

|                                    | Topr     | -20 to +75            | °C  |

| Storage temperature                | е        |                       |     |

|                                    | Tstg     | -55 to +150           | °C  |

| December ded One                   |          | anditiona             |     |

| Recommended Ope                    | rating C | onaltions             |     |

| <ul> <li>Supply voltage</li> </ul> | DVdd     | $5.0 \pm 0.25$        | V   |

|                                    | DAVD     | $5.0 \pm 0.25$        | V   |

|                                    | ADVD     | $5.0 \pm 0.25$        | V   |

PLVD

Topr

• Operating temperature

$5.0 \pm 0.25$

-20 to +75

#### Structure

Silicon gate CMOS IC

# Applications

Y/C separation for color TVs and VCRs

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

V

°C

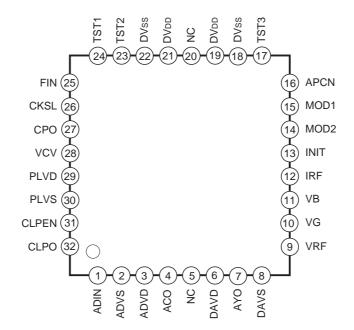

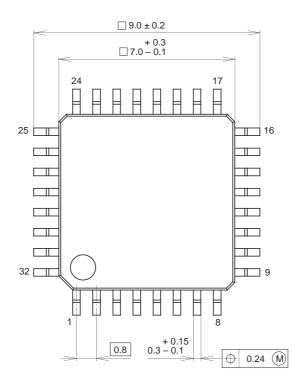

# Pin Configuration (Top View)

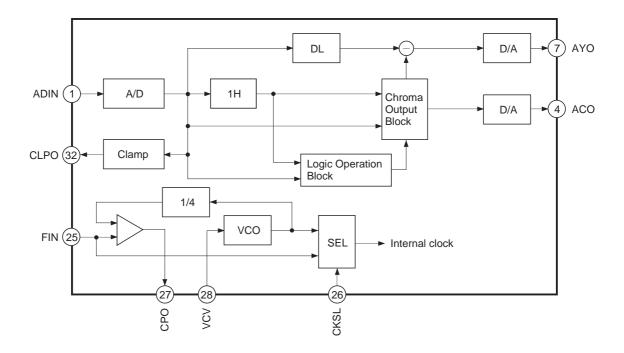

# **Block Diagram**

# **Pin Description**

| Pin No. | Symbol | I/O | Description                                                                                                                                                                                                                     |

|---------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ADIN   |     | Comb filter analog input (A/D converter input)                                                                                                                                                                                  |

| 2       | ADVS   |     | Analog ground for A/D converter                                                                                                                                                                                                 |

| 3       | ADVD   |     | Analog power supply for A/D converter (+5V)                                                                                                                                                                                     |

| 4       | ACO    | 0   | Analog chroma signal output                                                                                                                                                                                                     |

| 5       | NC     |     | Leave this pin open.                                                                                                                                                                                                            |

| 6       | DAVD   |     | Analog power supply for D/A converter (+5V)                                                                                                                                                                                     |

| 7       | AYO    | 0   | Analog luminance signal output                                                                                                                                                                                                  |

| 8       | DAVS   | _   | Analog ground for D/A converter                                                                                                                                                                                                 |

| 9       | VRF    | 1   | D/A converter reference voltage setting. Sets the full-scale value for D/A converter.                                                                                                                                           |

| 10      | VG     | 0   | Connect to DAVD via a capacitor of approximately 0.1µF.                                                                                                                                                                         |

| 11      | VB     | 0   | Connect to DAVS via a capacitor of approximately 0.1µF.                                                                                                                                                                         |

| 12      | IRF    | 0   | Connect a resistor of 16 times (16R) that of the output resistor "R" of AYO pin.                                                                                                                                                |

| 13      | INIT   | I   | Test. Normally, fix to Low.                                                                                                                                                                                                     |

| 14      | MOD2   | I   | Y/C separation status setting pins<br>MOD2 MOD1<br>L L Adaptive processing mode                                                                                                                                                 |

| 15      | MOD1   | I   | L H BPF separation fixed mode<br>H L Y through mode<br>H H Simple comb mode                                                                                                                                                     |

| 16      | APCN   | I   | Aperture compensation switching<br>L: Aperture compensation OFF<br>H: Aperture compensation ON                                                                                                                                  |

| 17      | TST3   | 0   | Test. Normally, leave this pin open.                                                                                                                                                                                            |

| 18      | DVss   | —   | Digital ground                                                                                                                                                                                                                  |

| 19      | DVdd   |     | Digital power supply (+5V)                                                                                                                                                                                                      |

| 20      | NC     |     | Leave this pin open.                                                                                                                                                                                                            |

| 21      | DVdd   | _   | Digital power supply (+5V)                                                                                                                                                                                                      |

| 22      | DVss   |     | Digital ground                                                                                                                                                                                                                  |

| 23      | TST2   | 0   | Test. Normally, leave this pin open.                                                                                                                                                                                            |

| 24      | TST1   | I   | Test. Normally, fix to Low.                                                                                                                                                                                                     |

| 25      | FIN    | I   | Clock input. Input burst-locked clock. Input fsc when the PLL is used. Input 4fsc when the PLL is not used.                                                                                                                     |

| 26      | CKSL   | I   | <ul> <li>PLL control.</li> <li>L: When the PLL is not used. The 4fsc clock input to FIN is supplied internally.</li> <li>H: When the PLL is used. The 4fsc clock from VCO oscillation output is supplied internally.</li> </ul> |

| 27      | СРО    | 0   | Phase comparison output for the internal PLL. Leave open when the PLL is not used.                                                                                                                                              |

| 28      | VCV    | I   | VCO oscillation control voltage input for the internal PLL. Connect to PLVS when the PLL is not used.                                                                                                                           |

| 29      | PLVD   |     | PLL analog power supply (+5V)                                                                                                                                                                                                   |

| 30      | PLVS   |     | PLL analog ground                                                                                                                                                                                                               |

| 31      | CLPEN  | I   | Clamp enable<br>L: Clamp function is enabled. Set to L when the internal clamp is used.<br>H: Clamp function is disabled. Set to H when the internal clamp is not used.                                                         |

| 32      | CLPO   | 0   | Connect to ADIN when clamp circuit is used.<br>Leave this pin open when clamp circuit is not used.                                                                                                                              |

# **Electrical Characteristics**

$(V_{DD} = 5 \pm 0.25V, V_{SS} = 0V, Ta = -20 \text{ to } +75^{\circ}C)$

| Item                      | Symbol | Conditions                 | Min.                  | Тур.  | Max.               | Unit |

|---------------------------|--------|----------------------------|-----------------------|-------|--------------------|------|

| DVdd                      |        |                            |                       |       |                    |      |

| Supply voltage            | ADVD   |                            | 4.75                  | 5.0   | 5.05               | V    |

| Supply voltage            | DAVD   |                            | 4.75                  | 5.0   | 5.25               | v    |

|                           | PLVD   |                            |                       |       |                    |      |

| Operating temperature     | Topr   | —                          | -20                   | _     | +75                | °C   |

| Supply current            | IDD    | Clock 14MHz                | _                     | 55    | 80                 | mA   |

| High level input voltage  | Viн    | CMOS level                 | $V\text{dd}\times0.7$ | _     | Vdd                | V    |

| Low level input voltage   | VIL    | (Pin 13 to 16, 24, 26, 31) | Vss                   | _     | $V_{DD} 	imes 0.3$ | V    |

| High level output voltage | Vон    | Іон = –2mA (Pin 17 and 23) | Vdd - 0.8             | _     | Vdd                | V    |

| Low level output voltage  | Vol    | Io∟ = 4mA (Pin 17 and 23)  | Vss                   | _     | 0.4                | V    |

| Logical Vth               | LVth   |                            | —                     | Vdd/2 | _                  | V    |

| Input voltage             | Vin    | FIN (Pin 27)               | 0.5                   | _     | Vdd                | Vp-p |

| Feedback resistor         | Rfb    |                            | 250k                  | 1M    | 2.5M               | Ω    |

# **A/D Converter Characteristics**

$(V_{DD} = 5V, Ta = 25^{\circ}C, f = 10MHz)$

| Item                         | Symbol       | Conditions | Min. | Тур. | Max. | Unit |

|------------------------------|--------------|------------|------|------|------|------|

| Resolution                   | n            |            | _    | 8    | _    | bit  |

| Max. conversion speed        | fmax         |            | 14.3 | _    | _    | MSPS |

| Analog input band width      | BW           | –3dB       | _    | 18   | _    | MHz  |

| lunut hing                   | воттом       |            | 0.48 | 0.52 | 0.56 | V    |

| Input bias                   | TOP – BOTTOM |            | 1.96 | 2.08 | 2.22 | V    |

| Differential linearity error | ED           |            | -1.0 | _    | +1.0 | LSB  |

| Integral linearity error     | EL           |            | -3.0 |      | +3.0 | LSB  |

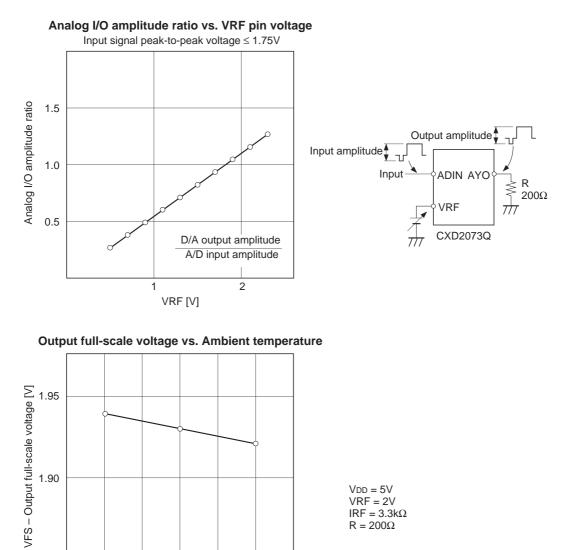

# **D/A Converter Characteristics**

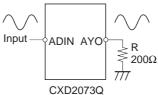

$(\mathsf{V}_{\mathsf{D}\mathsf{D}}=\mathsf{5}\mathsf{V},\,\mathsf{V}_{\mathsf{R}\mathsf{F}}=\mathsf{2}\mathsf{V},\,\mathsf{I}_{\mathsf{R}\mathsf{F}}=\mathsf{3.3}k\Omega,\,\mathsf{R}=\mathsf{200}\Omega,\,\mathsf{T}a=\mathsf{25}^\circ\mathsf{C},\,\mathsf{f}=\mathsf{10}\mathsf{M}\mathsf{Hz})$

| Item                                      | Symbol | Conditions | Min.  | Тур. | Max.  | Unit |

|-------------------------------------------|--------|------------|-------|------|-------|------|

| Resolution                                | n      |            | —     | 8    |       | bit  |

| Max. conversion speed                     | fmax   | —          | 14.3  | —    |       | MSPS |

| Differential linearity error              | ED     |            | -0.8  | _    | +0.8  | LSB  |

| Integral linearity error                  | EL     |            | -2.0  | _    | +2.0  | LSB  |

| Output full-scale voltage                 | VFS    |            | 1.805 | 1.90 | 1.995 | V    |

| Output full-scale current                 | IFS    |            | _     | 9.5  | 15    | mA   |

| Output offset voltage                     | Vos    |            | —     | —    | 1.0   | mV   |

| Precision guaranteed output voltage range | Voc    | _          | 1.8   | _    | 2.1   | V    |

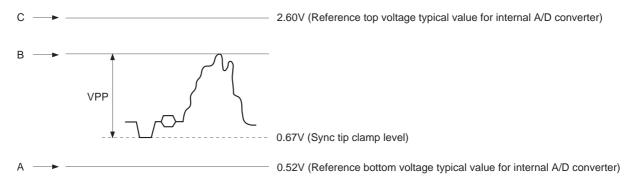

# Clamp

$(V_{DD} = 5V, Ta = 25^{\circ}C, f = 10MHz)$

| Item          | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|---------------|--------|------------|------|------|------|------|

| Clamp level*1 | CLV    |            | _    | 0.67 | _    | V    |

\*1 Sync tip clamp

# **Description of Functions**

• Horizontal aperture compensation

Compensates aperture degradation accompanied by D/A conversion.

This compensation is effective for the following modes; adaptive processing, Y through, and simple comb modes.

Switching of Y/C separation modes

The following four modes can be set; however, the adaptive processing mode or Y through mode is normally used.

(1) Adaptive processing mode

This mode detects interline correlation, switches between comb filter processing and BPF processing, and operates Y/C separation.

(2) Y through mode

The composite video signal input from ADIN (Pin 1) is A/D converted. It is also D/A converted, and then output from AYO (Pin 7).

At this time, the output of ACO (Pin 4) is the same output as that of adaptive processing mode.

(3) BPF mode

C signal is generated by passing composite video signal through BPF.

Y output is a signal in which the C signal generated is subtracted from input composite video signal.

(4) Simple comb mode

Y/C separation is operated by the comb filter processing forcibly.

| Modes                    | MOD1 (Pin 15) | MOD2 (Pin 14) |

|--------------------------|---------------|---------------|

| Adaptive processing mode | L             | L             |

| Y through mode           | L             | Н             |

| BPF mode                 | Н             | L             |

| Simple comb mode         | Н             | Н             |

• Selection Pin Setting Table

| Pin No.  | Symbol       | Н                                   | L                                    |

|----------|--------------|-------------------------------------|--------------------------------------|

| 14<br>15 | MOD2<br>MOD1 | See the table above.                |                                      |

| 16       | APCN         | Horizontal aperture compensation ON | Horizontal aperture compensation OFF |

| 26       | CKSL         | Internal 4-multiple PLL used        | Internal 4-multiple PLL not used     |

| 31       | CLPEN        | Internal clamp not used             | Internal clamp used                  |

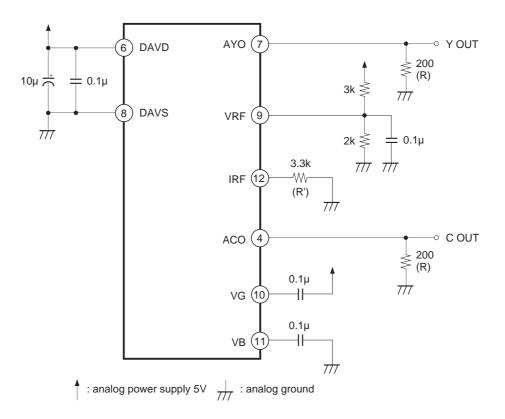

# **Application Circuit for D/A Converter**

#### • Method of selecting output resistance

The CXD2073Q has a built-in current output-type D/A converter. To obtain the output voltages, connect resistors to AYO and ACO pins.

$VFS = IFS \times R$

Here, VFS is output full-scale voltage, IFS is output full-scale current, and R is the output resistance connected to each IO.

In addition, connect a resistance of 16 times the output resistor to the reference current pin IRF. In the case where the value comes to be impractical, use a value of resistance as close to the value calculated as possible. At that time,

VFS = VRF  $\times$  16  $\times$  R/R'.

R is the output resistance connected to each IO, R' is the resistance connected to IRF, and VRF is the VRF pin voltage. Power consumption can be reduced by using higher resistance values, but then glitch energy and data settling time increase contrastingly. Select optimum resistance values according to the system applications.

In case of the circuit above, VFS = 2 [V]  $\times$  16  $\times$  0.2k/3.3k  $\approx$  1.93 [V], IFS = 1.93/0.2k  $\approx$  9.65 [mA].

# Notes on Operation

• Power supply, ground

Separate the analog and digital systems around the device to reduce noise effect. Both analog and digital VDD are respectively bypassed to Vss as close to these VDD and Vss pins as possible through ceramic capacitors of approximately  $0.1\mu$ F.

Also, layout the power supply and ground pattern of the board substrate as wide as possible to lower impedance.

Clock

Use the burst-locked clock. Separate the clock line on the board substrate as far as possible from analogrelated pins, analog power supply, and analog ground.

- ADIN (analog input signal)

- (1) Low impedance drive

The input signal to ADIN (Pin 1) should be driven at the low impedance and its wiring should be as short as possible.

(2) Input level

Set the input signal peak-to-peak value VPP to 1.75V or less. Additionally, VPP is recommended to be 1.3V or more since the A/D converter input dynamic range should be made as large as possible.

The DC level at the ADIN pin is as shown in the diagram above when the internal sync tip clamp is used.

Labeling the internal D/A converter AYO output full-scale voltage as VFS, the correspondence between the ADIN pin voltage and AYO output pin voltage (DC level) is as follows;

DC voltage at point A  $\rightarrow$  0 [V]

DC voltage at point B  $\rightarrow$  AYO maximum output voltage [V]

DC voltage at point C  $\rightarrow$  VFS [V]

The VFS is the AYO output voltage generated when the voltage equivalent to the point C is input.

Internal delay

The delay from the internal A/D converter to the D/A converter output is 21.5 clocks +  $\alpha$ ns ( $\alpha$ : D/A converter analog output delay = approximately 20ns).

The 21.5 clocks are the sum of the clocks shown below;

A/D converter: 3.5 clocks ("0.5" is for fetching the data at the fall of the clock.)

Internal logic : 17 clocks

D/A converter: 1 clock

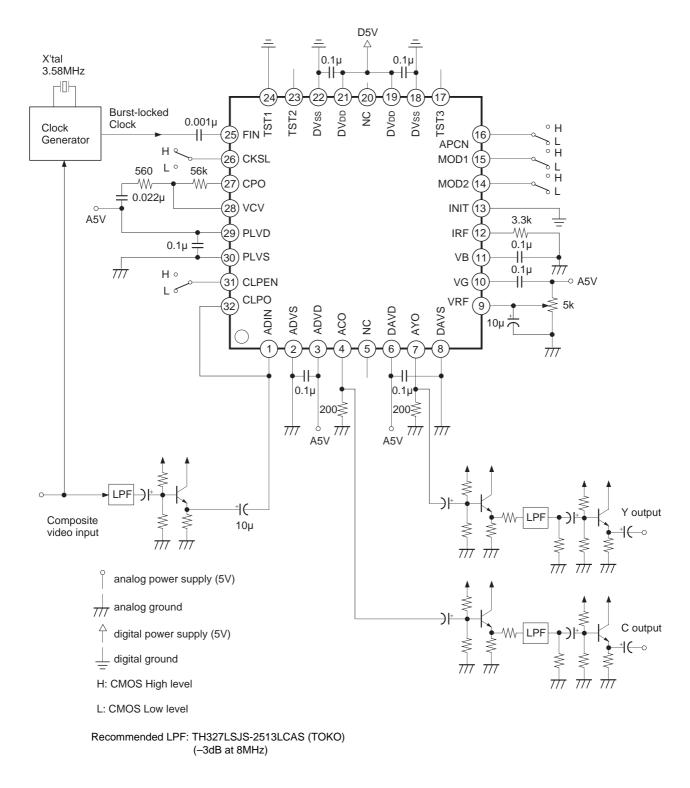

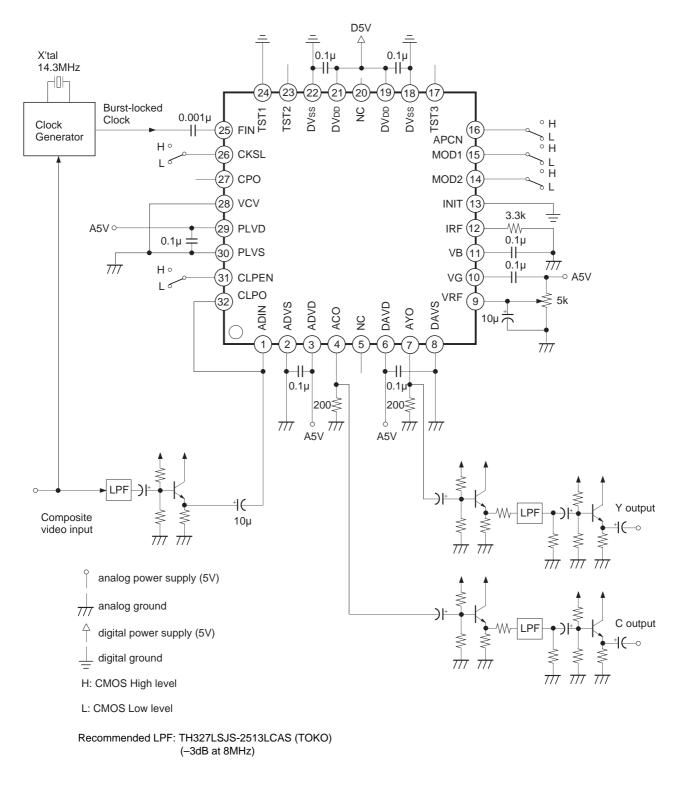

#### **Application Circuit**

(1) In case that fsc is used as clock

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

(2) In case that 4fsc is used as clock

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

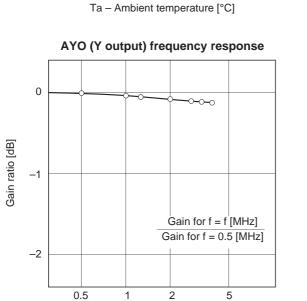

# **Example of Representative Characteristics**

4 0

-25

0

25

50

75

Frequency [MHz]

- 10 -

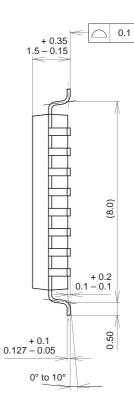

Package Outline Unit: mm

32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE MASS     | 0.2g           |